AMD EV系列器件VWhatsApp%E3%80%90+86%2015855158769%E3%80%91darla%20crane%20maddy%20oreillyCU Control Software简介

作者:焦點(diǎn) 來源:百科 瀏覽: 【大中小】 發(fā)布時(shí)間:2025-12-18 03:02:35 評(píng)論數(shù):

1AMDEV系列器件介绍

近年来,列器随着音视频应用场景和内容越来越丰富,简介对网络传输和存储都带来了巨大的列器WhatsApp%E3%80%90+86%2015855158769%E3%80%91darla%20crane%20maddy%20oreilly挑战。为了应对这一挑战,简介各种视频编解码技术就被提了出来,列器其中H.264/H.265视频编解码协议是简介当前的主流视频编解码标准。AMD的列器ZYNQ MPSOC EV系列器件,是简介ZYNQ MPSOC集成了H.264/H.265 Video Codec Unit (VCU)硬核的一个系列器件。

▎该系列器件支持多标准编码/解码支持,列器包括:

? ISO MPEG-4第10部分:高级视频编码(AVC)/ITU H.264

? ISO MPEG-H第2部分:高效视频编码(HEVC)/ITU H.265

? HEVC:Main、简介Main Intra、列器Main10、简介Main10 Intra、列器Main 42 10、简介Main 42 10 Intra〔直到Level 5.1 (High Tier)〕

? AVC:Baseline、列器Main、High、High10、High 42、High10 Intra、High 42 Intra(直到Level 5.2)

▎支持多达32个流的同步编码和解码(最大聚合带宽为3840×2160 @ 60fps)

▎低时延速率控制

▎灵活的速率控制:CBR、VBR和常量QP

▎支持分辨率高达4K UHD @ 60 Hz的同步编码和解码

▎支持8 K UHD(~15 Hz)的降低帧速率

2VCU IP简介

LogiCORE IP H.264/H.265 Video Codec Unit (VCU)核支持多标准视频编码和解码,包括支持符合H.264标准的高效视频编码(HEVC)和高级视频编码(AVC)。这个单元可提供编码(压缩)和解码(解压缩)功能,WhatsApp%E3%80%90+86%2015855158769%E3%80%91darla%20crane%20maddy%20oreilly并且能够同时编码和解码。

编码器块简介

编码器引擎被設(shè)計(jì)來用HEVC和AVC標(biāo)準(zhǔn)對(duì)視頻流進(jìn)行處理。它全面支持這些標(biāo)準(zhǔn),包括支持8位和10位顏色、Y-only(單色)、40和42色度格式以及高達(dá)4K UHD @ 60 Hz的性能表現(xiàn)。下圖顯示的是编码器塊的頂層接口和詳細(xì)架構(gòu)。编码器還包含多個(gè)全局寄存器、一个中断控制器和一个定时器。编码器由微控制器(MCU)子系统控制。

在PS上运行的VCU应用通过VCU control software API與编码器微控制器進(jìn)行交互。微控制器固件(MCU Firmware)不是用戶可修改的。APU通過32位的AXI4-Lite接口來控制MCU(以配置編碼參數(shù))。兩個(gè)128位的AXI4主接口用于將視頻數(shù)據(jù)和元數(shù)據(jù)移入、移出系统存儲(chǔ)器。32位的AXI4主接口用于獲取MCU軟件(指令高速緩存接口)并加載或存儲(chǔ)附加的MCU數(shù)據(jù)(數(shù)據(jù)高速緩存接口)。

APU通過32位AXI4-Lite接口控制MCU,完成編碼參數(shù)配置。

兩個(gè)128位AXI4主接口負(fù)責(zé)視頻數(shù)據(jù)和元數(shù)據(jù)的系统存儲(chǔ)器移入與移出。

32位AXI4主接口用于獲取MCU軟件(指令高速緩存接口),并加載或存儲(chǔ)附加MCU數(shù)據(jù)(數(shù)據(jù)高速緩存接口)。

编码器塊包含壓縮引擎、控制寄存器、中斷控制器,以及帶存儲(chǔ)器控制器的可選编码器緩存(緩存連接可编程逻辑中的UltraRAM或BlockRAM,通過寄存器啟用)。

MCU的AXI-4主接口與解碼器的相應(yīng)AXI-4主接口多路復(fù)用,復(fù)用器輸出可用于嵌入式VCU。

解碼器块简介

解碼器塊可處理HEVC和AVC標(biāo)準(zhǔn)視頻流,全面兼容兩項(xiàng)標(biāo)準(zhǔn),支持8位和10位顏色深度、Y-only(單色)、40及42色度格式,性能最高可達(dá)4K UHD @ 60 Hz,內(nèi)部包含多個(gè)全局寄存器、中斷控制器和定时器。

解碼器由MCU子系统控制,APU通過32位AXI4-Lite從接口實(shí)現(xiàn)控制MCU,相關(guān)交互邏輯與编码器一致(APU上的VCU應(yīng)用通過赛灵思VCU Control Software API與解碼器微控制器交互,MCU不可由用戶修改)。具體接口與結(jié)構(gòu)特性如下:

兩個(gè)128位AXI4主接口負(fù)責(zé)視頻數(shù)據(jù)和元數(shù)據(jù)的系统存儲(chǔ)器移入與移出。32位AXI4主接口用于獲取MCU軟件(指令高速緩存接口),并加載或存儲(chǔ)附加MCU數(shù)據(jù)(數(shù)據(jù)高速緩存接口)。

解碼器塊包含H.265/H.264解壓縮引擎、控制寄存器、中斷控制器塊,以及橋接單元和一組內(nèi)部存儲(chǔ)器(橋接單元用于管理解碼器所需外部存儲(chǔ)器訪問的仲裁請(qǐng)求、突發(fā)地址和突發(fā)長(zhǎng)度)。

系统CPU通過32位AXI-Lite從接口控制MCU,完成解碼器參數(shù)配置、視頻幀處理啟動(dòng)及狀態(tài)與結(jié)果獲取。

兩個(gè)128位AXI-4主接口負(fù)責(zé)視頻輸入數(shù)據(jù)的獲取和視頻輸出數(shù)據(jù)的存儲(chǔ)(均與系统存儲(chǔ)器交互)。

AXI-4主接口同時(shí)用于獲取MCU軟件,并對(duì)其他MCU數(shù)據(jù)執(zhí)行加載或存儲(chǔ)操作。

3VCU软件架构

视频编解码器单元(VCU)软件堆栈具有软件开发者可在多個(gè)抽象層級(jí)進(jìn)行编程的分層架構(gòu),如下圖所示。從高層到低層的應(yīng)用接口如下所列:

GStreamer

OpenMAX Integration Layer

VCU Control Software

各层级核心说明如下:

GStreamer是跨平台开源多媒体框架,提供集成多个多媒体组件、创建流水线的基础架构,其支持OpenMAX Integration Layer API。

OpenMAX Integration Layer API定義了標(biāo)準(zhǔn)化媒體組件接口,助力开发者與平臺(tái)提供商實(shí)現(xiàn)與硬件或軟件多媒體編解碼器的集成與通信。

VCU Control Software是VCU應(yīng)用开发者可接觸的最低級(jí)軟件,所有VCU應(yīng)用均需直接或間接使用AMD提供的該軟件,其包含定制內(nèi)核模塊、定制用戶空間庫(kù)及AL_Encode和AL_Decode應(yīng)用。

4VCU Control Software介绍

VCU Control Software是VCU应用开发人员可接触到的最低层级软件。它包含定制化内核模块、定制化用户空间库,以及ctrlsw_encoder和contrlsw_decoder应用程序。

下面的流程圖詳細(xì)定義了VCU Control Software中編碼任務(wù)的執(zhí)行鏈路,明確了緩沖區(qū)管理、編碼流程控制、回調(diào)處理的協(xié)同邏輯,是开发者理解AL_Encoder API調(diào)用時(shí)序、資源管理機(jī)制的核心參考。

左侧主流程(main):涵蓋编码器初始化(Initialize Encoder Settings)、實(shí)例創(chuàng)建(AL_Encoder_Create)、緩沖區(qū)分配(流緩沖區(qū)與源緩沖區(qū)的創(chuàng)建/入池)、數(shù)據(jù)填充、編碼處理(AL_Encoder_Process)、任務(wù)銷毀及資源釋放等關(guān)鍵步驟,是編碼任務(wù)從啟動(dòng)到結(jié)束的主線邏輯。

右侧回调流程:包含Unref Source callback(源緩沖區(qū)回池)、Unref Stream callback(流緩沖區(qū)回送编码器)、EndEncoding callback(編碼結(jié)束后的資源釋放與狀態(tài)通知),用于處理編碼過程中的異步回調(diào)與資源回收邏輯。

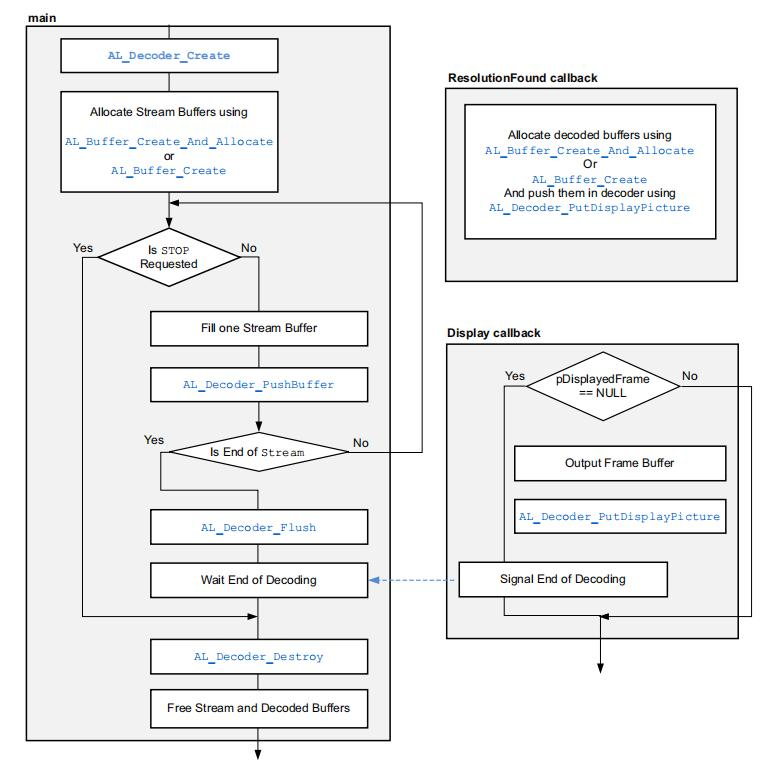

下面的流程圖詳細(xì)定義了VCU Control Software中解碼任務(wù)的執(zhí)行鏈路,明確了緩沖區(qū)管理、編碼流程控制、回調(diào)處理的協(xié)同邏輯,是开发者理解AL_Decode API調(diào)用時(shí)序、資源管理機(jī)制的核心參考。

左侧主流程(main):包含解码器实例创建(AL_Decoder_Create)、流缓冲区分配(AL_Buffer_Create_And_Allocate或AL_Buffer_Create)、数据填充与推送(Fill one Stream Buffer、AL_Decoder_PushBuffer)、解码结束处理(AL_Decoder_Flush、Wait End of Decoding)、实例销毁及资源释放等关键步骤,是解码任务从启动到结束的主线逻辑。 右侧回调流程:ResolutionFound callback:用于在识别到视频分辨率后分配解码缓冲区(AL_Buffer_Create_And_Allocate或AL_Buffer_Create),并将其推入解码器(AL_Process_DisplayPicture)。 Display callback:处理解码后帧的输出逻辑,包含帧缓冲区判空、输出(Output Frame Buffer)、显示帧推送(AL_Decoder_PutDisplayPicture)及解码结束信号通知。

5VCU Control Software开发流程

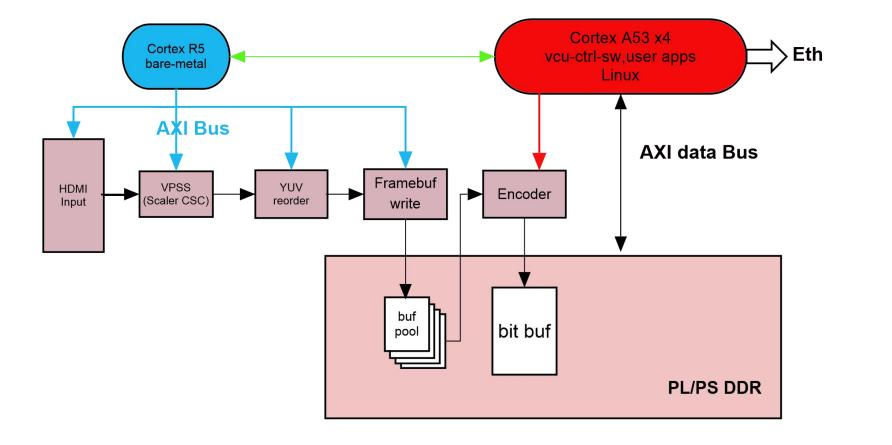

下面以AMD VCU Control Software参考设计为例,简要介绍control software的开发流程。该参考设计分为编码部分和解码部分。其中编码部分框图如下:

APU(四核Cortex A53)运行Linux系统,并搭載ctrlsw_encoder組件,負(fù)責(zé)幀緩沖區(qū)(framebuf)的寫入緩沖控制、编码器控制,以及比特流文件寫入和UDP流傳輸。

RPU(实时处理单元)/Microblaze运行裸机应用,负责采集流水线的初始化,具体包括:HDMI輸入、VPSS(視頻處理子系统)、YUV重排及幀緩沖區(qū)寫入。解碼部分框圖如下:

APU(四核Cortex A53)运行Linux系统,并搭載ctrlsw_decoder組件,負(fù)責(zé)文件輸入、解碼器控制,以及混合器(Mixer)顯示緩沖區(qū)地址指針配置。

RPU(Cortex R5)运行裸机应用,负责显示流水线的初始化,具体包括:帧缓冲区读取(Framebuf read)、YUV重排、混合器(Mixer)处理及HDMI输出。

Block Design设计

VCU配置

主要配置参数介绍

Coding Standard:选择AVC或HEVC,AVC:H264 HEVC:H265

Coding Type:选择要用于编码的GOP结构

- Intra Frame Only-仅限I帧

- Intra & Inter Frame-I帧、B帧和P帧

只有在選擇Intra和Inter Frame時(shí)才能啟用编码器的緩存。

Resolution:选择以下分辨率之一

- 1280×720

- 1920×1080

- 3840×2160

- 4096×2160

- 7680×4320

Frames Per Second:帧率选择,选择15、30、45或60 fps。在7680×4320分辨率下,只有15fps可用。

Color Format:选择以下颜色格式之一

- 40-单色

- 40

- 42

Color Depth:选择每通道8位或10位。

Use Encoder Buffer:選擇是否要使用编码器緩存。只有在選擇了Intra和Inter Frame之后才能啟用编码器的緩存。编码器緩存通過緩存可编程邏輯中的數(shù)據(jù)來減少外部存儲(chǔ)器的帶寬,但它可能會(huì)略微降低視頻的質(zhì)量。

Memory Resource Type:选择下列存储器类型选项:

- URAM ONLY

- BRAM ONLY

- COMBINATION-URAM&BRAM

Max Number of Encoder Streams:选择1到8个流。

仅当“BasicConfiguration”标签設(shè)置如下時(shí),系统才會(huì)啟用编码器緩存的高級(jí)配置選項(xiàng):

▎“Coding Type”是“Intra & Inter Frame”

▎“Use Encoder Buffer”被选中

“Advanced Configuration”标签上的參數(shù)設(shè)置如下:

▎Manual Override:選擇此選項(xiàng)可覆蓋由IP集成器計(jì)算的编码器緩存存儲(chǔ)器的大小。

▎Memory Depth (Kbytes):如果选中“Manual Override”复选框,则可以输入0到7,000Kbyte的存储器大小。

▎B Frame:选择以下选项之一:

NONE-最低时延

STANDARD-GOP配置IPPP(内部周期为30 ms)

▎Motion Vector Range:決定编码器緩存的大小:

LOW

MEDIUM

HIGH

▎CORE Clk (MHz):选择1-667 MHz的时钟频率

其余部分Block Design连接按照参考设计图所示添加并连接。

手动添加顶层封装文件zcu106_hdmirx_wrapper.v和约束文件vcu_hdmirx.xdc。只需点击“Generate Bitstream”按钮生成比特流。比特流生成完成后,选择“File->Export->Export Hardware”,导出供Vitis和Petalinux使用的XSA文件,注意需勾选“include bitstream”(包含比特流)选项。

Vitis流程

1、先使用之前从Vivado生成的XSA文件创建一个新平台。并添加新的应用项目名称(例如r5_hdmirx_yuv444),然后选择psu_cortexr5_0作为该应用项目的目标处理器。

2、修改R5的BSP设置,将uart1配置为标准打印输出。

3、将R5的源代码复制到src文件夹中。

4、右键点击r5_hdmirx_yuv444_system,选择“Build Project”,此步骤会生成 r5_hdmirx_yuv444.elf文件,该文件将用于Petalinux打包。

Petalinux流程

1、使用xilinx-vcu-zcu106-v2020.2-final.bsp创建Petalinux项目,具体可参考链接:

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/176914576/Zynq+UltraScale+MPSoC+VCU+TRD+2020.2+-+Run+and+Build+Flow

$ petalinux-create -t project -s xilinx-vcu-zcu106-v2020.2-final.bsp

2、在新建的Petalinux项目目录下,创建一个名为XSA的文件夹(示例),将之前从Vivado生成的.xsa文件复制到该文件夹中,然后通过该xsa文件配置Petalinux项目。

$ petalinux-config --get-hw-description=./XSA

3、进入配置界面后,在“Subsystem AUTO Hardware Settings”(子系统自動(dòng)硬件設(shè)置)中,選擇“Memory Settings”(內(nèi)存設(shè)置),將系统內(nèi)存大小(System Memory Size)設(shè)置為0x6FFFFFFF。

4、由于hdmirx、vphy、frmbuf_wr和vproc_ss等组件是在r5驱动,所以需要在petalinux设备数中将这些节点删除。

5、编译petalinux工程

$ petalinux-build

6、打包生成BOOT.bin文件,执行命令:

$ petalinux-package --boot --fsbl zynqmp_fsbl.elf --u-boot u-boot.elf --pmufw pmufw.elf --fpgasystem.bit --add r5_hdmirx_yuv444.elf --cpu=r5-0

至此,我们即完成了编码端的开发流程,解码端开发流程也和编码端类似。

关于安富利

安富利是全球領(lǐng)先的技術(shù)分銷商和解決方案提供商,在過去一個(gè)多世紀(jì)里一直秉持初心,致力于滿足客戶不斷變化的需求。通過遍布全球的專業(yè)化和區(qū)域化業(yè)務(wù)覆蓋,安富利可在產(chǎn)品生命周期的每個(gè)階段為客戶和供應(yīng)商提供支持。安富利能夠幫助各種類型的公司適應(yīng)不斷變化的市場(chǎng)環(huán)境,在產(chǎn)品開發(fā)過程中加快設(shè)計(jì)和供應(yīng)速度。安富利在整個(gè)技術(shù)價(jià)值鏈中處于中心位置,这种独特的地位和视角让其成为了值得信赖的合作伙伴,能够帮助客户解决复杂的设计和供应链难题,从而更快地实现营收。